1. Introduction

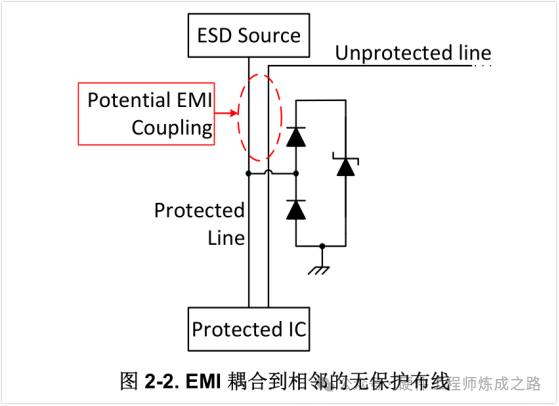

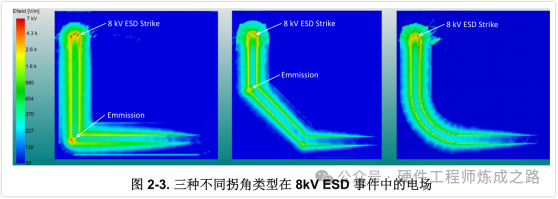

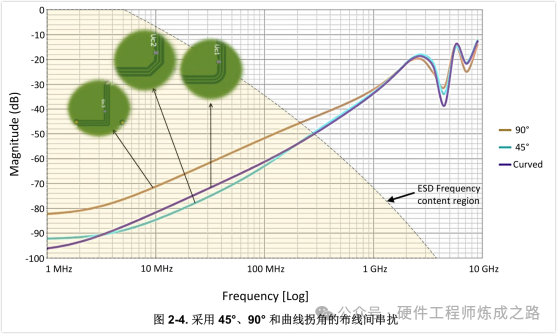

Another issue arising from the rapidly changing IESD is that its associated rapidly changing electromagnetic field (EM) can cause interference (EMI) to couple to other circuits on the PCB, especially in the area between the ESD source and TVS. Once the TVS diverts the IESD to ground, the wiring between the TVS and the protected IC should be relatively unaffected by EMI. Therefore, between the ESD source and TVS, unprotected circuits should not be adjacent to the wiring of the ESD protection circuit. In order to minimize EMI radiation, ideally, the circuit wiring between the ESD source and TVS should not have corners exceeding 45 degrees or curves with large radii.

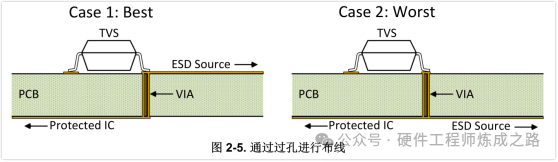

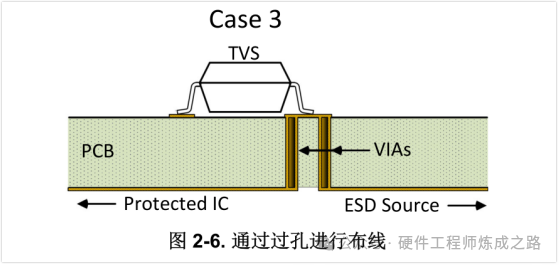

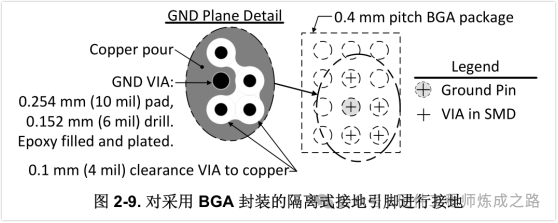

In today's PCB layout, board space is very valuable. IC, Including TVS, they must be designed very compactly. In addition, the placement density of ICs on PCBs is constantly increasing. Multilayer PCB circuit boards and wiring heavily rely on via holes to maximize density, thereby reducing system size and increasing system feature settings. This PCB architecture (especially related to layer switching and via) plays an important role in diverting IESD to ground through TVS. The use of via holes to wire circuits to TVS may result in significant VESD voltage differences on the protected IC. Usually, placing a via between the ESD source and TVS has adverse effects, but in some cases, designers may have to resort to this strategy. Even in the above situations, if handled properly, VESD can still be minimized on the protected IC as much as possible.

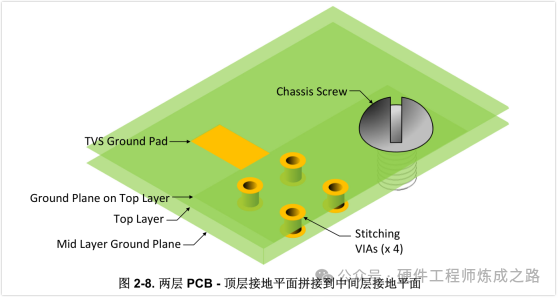

The grounding scheme is crucial for preventing ESD. Using chassis grounding for TVS (different from digital and/or analog grounding implemented by inductance) can effectively avoid ESD related failures. However, when wiring high-speed circuits on multiple grounding planes, this poses significant challenges. Therefore, many designs use a common ground for protected circuits. The grounding plane is essential for TVS to successfully consume IESD without increasing VESD. The electrical connection of the ground grounded chassis, such as the PCB grounding through-hole used for chassis screws, directly adjacent to the TVS grounding and ESD source grounding (such as the connector shielding layer), provides a reasonable method to keep the grounding offset at the protected IC to a minimum. If the system cannot utilize chassis ground grounding, tightly coupled multi-layer grounding planes can help keep ground drift at the protected IC to a minimum.

Summarizing these parameters, the factors that successfully protect the system from ESD impact include:

Control the impedance around TVS to consume ESD current IESD

Limit the impact of EMI on unprotected circuits

• Proper use of via to maximize ESD consumption by TVS

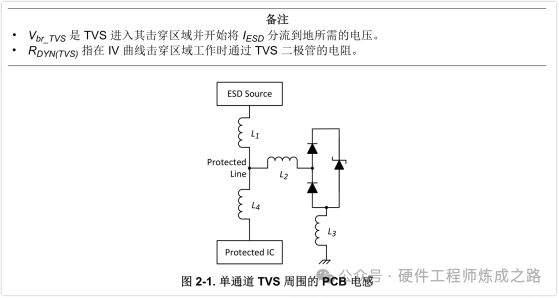

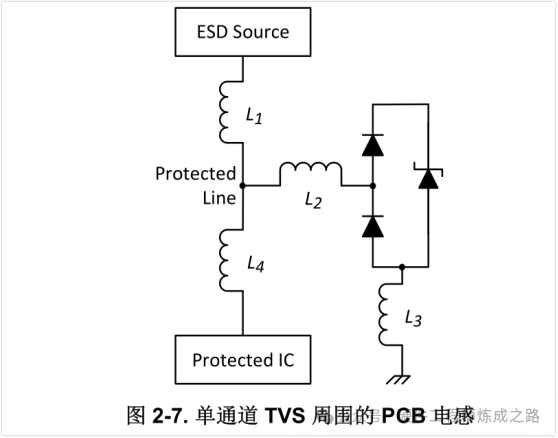

Without considering through holes, inductors L1 and L4 typically depend on design constraints, such as impedance controlled signal lines. However, by making L4 much larger than L1, IESD can still "turn" to TVS. This is achieved by placing the TVS near the ESD source and keeping the protected IC away from the TVS (such as near the middle of the PCB), as allowed by PCB design rules. This can effectively generate an effect of L4>>L1, helping to redirect IESD to TVS. Placing TVS close to the connector can also reduce EMI radiation into the system. In a well-designed system, the inductor at L2 should not exist. This indicates the presence of residual piles between TVS and the protected line. This design practice should be avoided. The protected circuit should be directly connected from the ESD source to the pins of TVS, ideally with no via on the path. The inductor at L3 represents the inductance between TVS and the ground terminal. The inductance value should be minimized as much as possible and may be the main parasitic effect affecting VESD.

The voltage provided to the "protected line" node will be VESD=Vbr-TVS+IESD RDYN (TVS)+(L2+L3) (dIESD/dt). Therefore, PCB designers need to minimize L3 and eliminate L2 as much as possible.

The method of minimizing L3 as much as possible is introduced in section 2.4. The method of minimizing L1 as much as possible is introduced in sections 2.2 and 2.3.

Summary

Minimize the inductance between the ESD source and the grounding path through TVS as much as possible

Place TVS near the connector, as allowed by design rules

Make the distance between the protected IC and TVS far exceed the distance from TVS to the connector

Do not use residual stakes between TVS and protected lines, wiring directly from ESD source to TVS

Do not place unprotected circuits in the area between the ESD source and TVS.

Place TVS near the connector, as allowed by design rules.

If possible, use straight wiring between the ESD source and TVS.

If corners must be used, curves should be preferred, and the maximum acceptable angle is 45 °.

2.3. Wiring through through-holes

Summary

• If possible, avoid via between ESD source and TVS

If a via is required between the ESD source and the protected IC, please wire directly from the ESD source to TVS before using the via

3. Conclusion

Control the impedance around TVS to dissipate ESD current IESD:

- Minimize the inductance between the ESD source and the grounding path through TVS as much as possible

- Place TVS near the connector, as allowed by design rules

Make the distance between the protected IC and TVS far exceed the distance from TVS to the connector.

- Do not use residual stakes between TVS and protected lines, wiring directly from ESD source to TVS

It is crucial to minimize the inductance between TVS and ground as much as possible

• Limit the impact of EMI on unprotected circuits:

- Do not place unprotected circuits in the area between the ESD source and TVS

- Place TVS near the connector, as allowed by design rules

- If possible, use straight wiring between ESD source and TVS

- If corners must be used, curves should be preferred, and the maximum acceptable angle is 45 °

• Use through-holes correctly to maximize ESD dissipation through TVS as much as possible:

- If possible, avoid using via between ESD source and TVS

If a via is required between the ESD source and the protected IC, please wire directly from the ESD source to TVS before using the via

• Use a grounding scheme with extremely low impedance: